- 您现在的位置:买卖IC网 > Sheet目录3891 > PIC18C801T-I/L (Microchip Technology)IC MCU ROMLESS A/D PWM 84PLCC

PIC18C601/801

DS39541A-page 104

Advance Information

2001 Microchip Technology Inc.

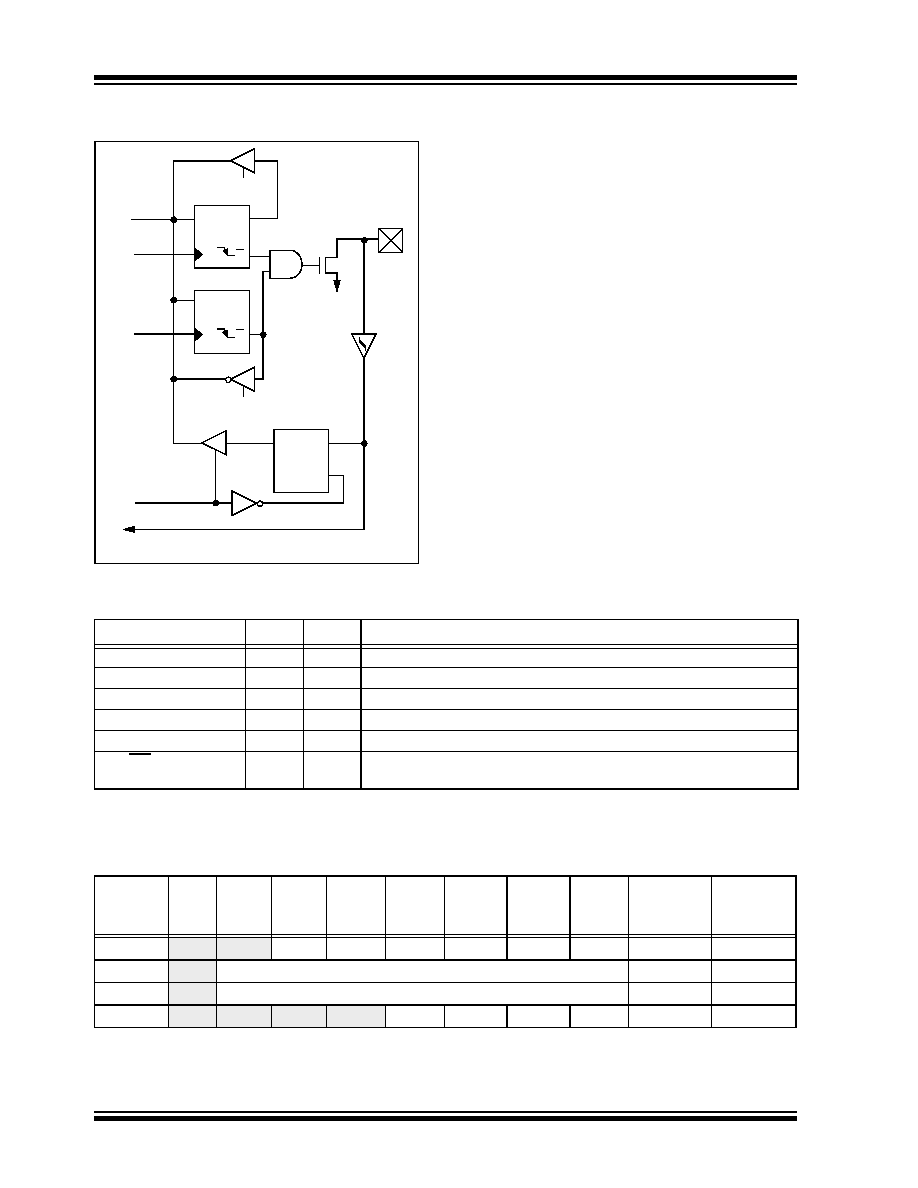

FIGURE 9-2:

RA4/T0CKI PIN BLOCK

DIAGRAM

TABLE 9-1:

PORTA FUNCTIONS

TABLE 9-2:

SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Data

Bus

WR TRISA

RD PORTA

Data Latch

TRIS Latch

RD TRISA

Schmitt

Trigger

Input

Buffer

N

VSS

I/O pin(1)

TMR0 Clock Input

Note 1: I/O pin has diode protection to VSS only.

Q

D

Q

CK

Q

D

Q

CK

EN

QD

EN

RD LATA

WR LATA

or

WR PORTA

Name

Bit#

Buffer

Function

RA0/AN0

bit0

TTL

Input/output or analog input

RA1/AN1

bit1

TTL

Input/output or analog input

RA2/AN2/VREF-

bit2

TTL

Input/output or analog input or VREF-

RA3/AN3/VREF+

bit3

TTL

Input/output or analog input or VREF+

RA4/T0CKI

bit4

ST/OD

Input/output or external clock input for Timer0, output is open drain type

RA5/SS/AN4/LVDIN

bit5

TTL

Input/output or slave select input for synchronous serial port or analog

input or low voltage detect input

Legend: TTL = TTL input, ST = Schmitt Trigger input, OD = Open Drain

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value on

POR,

BOR

Value on all

other

RESETS

PORTA

—

RA5

RA4

RA3

RA2

RA1

RA0

--0x 0000

--uu uuuu

LATA

—

Latch A Data Output Register

-xxx xxxx

-uuu uuuu

TRISA

—

PORTA Data Direction Register

-111 1111

ADCON1

—

VCFG1 VCFG0

PCFG3

PCFG2

PCFG1

PCFG0 --00 0000 --uu uuuu

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'.

Shaded cells are not used by PORTA.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18C658T-I/L

IC MCU OTP 16KX16 CAN 68PLCC

PIC18C658T-E/L

IC MCU OTP 16KX16 CAN 68PLCC

PIC16C925T-I/L

IC MCU OTP 4KX14 LCD DVR 68PLCC

PIC12F675-E/P

IC MCU CMOS 1K FLASH W/AD 8-DIP

PIC18C858T-E/L

IC MCU OTP 16KX16 CAN 84PLCC

PIC16F636-I/SL

IC PIC MCU FLASH 2KX14 14-SOIC

PIC18LC658T-I/L

IC MCU OTP 16KX16 CAN 68PLCC

PIC18LC801T-I/L

IC MCU ROMLESS A/D PWM 84PLCC

相关代理商/技术参数

PIC18C801T-I/PT

功能描述:8位微控制器 -MCU 2MB 1536 RAM 37I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858-E/L

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858-E/PT

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858EPT

制造商:MICRO CHIP 功能描述:New

PIC18C858-I/L

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858-I/PT

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858T-E/L

功能描述:8位微控制器 -MCU 40MHz 16K OTP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C858T-E/PT

功能描述:8位微控制器 -MCU 32KB 1536 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT